The brain is arguably the most important organ in the human body, managing and directing the function of all other systems, and turning the body’s collection of cells into a symphony of living matter.

While our neocortex and limbic brain get all the glory – controlling the elements that make us human, such as logic and creativity, emotion and memory – the reptilian brain regulates everything else, including our heart rate, our breathing, and our very consciousness, allowing all other aspects of the body to perform at their highest level.

Controllers are like the reptilian brains of the SD and microSD memory card—the unsung heroes responsible for commanding all core operations and ensuring the highest caliber of performance.

Controllers in SD

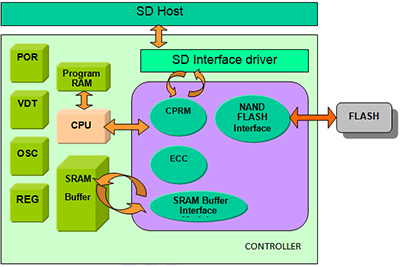

Controllers’ duties are vast. As the CPU of a laptop, controllers ensure every other component works properly. They serve as accelerators that speed up the computing of algorithms; enable error correcting code (ECC) engines to correct error bits; and allow the SD interface driver to handle commands from the host and the NAND interface driver to handle the data from the NAND flash.

Externally, they serve as the communication bridge between the host and the SD or microSD memory card, handling commands sent from the host and facilitating the responses from the card. And like a brain, a controller is an incredibly complicated device. It’s composed of four primary parts, but each of those comprises seemingly infinite subparts. Unlike the brain, however, smaller is better—but even as controllers shrink, the number of functions they have to support grows.

Like a building constructed out of LEGO bricks, controllers take on different characteristics based on what components have been built into them. If they contain a RAM buffer, for example, controllers can store data or a firmware management table temporarily. A different ECC engine—say, LDPC as opposed to BCH—will change their ability to correct error bits and alter the endurance of the same NAND flash.

A2 Adds Functions to Support

As eye-piercingly precise resolutions become the norm rather than the exception—first HD, now 4K, then 8K, and even 360˚—SD memory card performance must ensure that not one bit of data is lost or corrupted as it flows between card and camera, smartphone or laptop.

The introduction of App Performance Class 2 (A2) last spring dramatically raised the bar for SD memory cards, increasing IOPS read performance from 1500 to a minimum of 4000, and write performance from 500 to an astounding minimum bar of 2000, compared with A1, which had entered the market not long before.

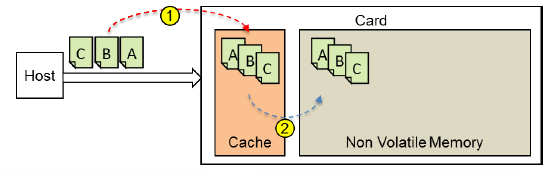

The command queue mechanism supports random read performance, so the card may accomplish tasks in the most efficient order. The cache function lets the card collect data in the RAM or SLC flash memory before writing it in the non-volatile TLC NAND flash memory, eliminating data loss with flush command. And the self-maintenance feature lets the card defragment whenever it needs to improve its performance.

None of this would be possible without controllers—the reptilian brain at the center of SD memory cards, quietly guiding their functions. A2 enables card speeds that are significantly faster than ever before, and that’s largely thanks to the way the controller manages the increased bandwidth and more efficient command management. All of those improvements are for naught without a controller that can handle them.

Controllers’ Role in A2

As stated, A2 adds functions to support, while the controller has to provide related hardware components to support these functions.

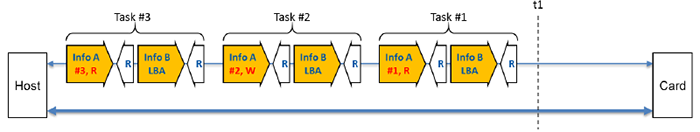

In the figure to the left (the controller structure), the controller has an SD interface driver to handle the task of command queue. In a command queue (the figure below), a host might use a voluntary CQ mode or sequential CQ mode. The SD interface driver is based on the task status (CMD13) and follows the priority to handle them (CMD46, CMD47). With the proper task controller by the SD interface driver, multiple tasks are handled at one time in arbitrary order. Moreover, the controller will locate the SRAM buffer to contribute high random performance by cache function, caching the host data during memory card access operations.

SRAM provides a cache to store temporary host data or tasks, and a CPU will handle these tasks in a cache while receiving new tasks simultaneously. The CPU and SD interface driver have to flush the cache within one second before the host powers off. Data might be lost during the flush processes, so the SD interface driver has to pull card in busy status to prevent the flush action from being interrupted, which would lead to data loss.

Controllers determine a product’s available capacity—so even if you upgrade the firmware, you need a larger management table and a greater number of die stacks in order to make the most of it.

It’s worth noting that upgrading controllers to boost availability comes at a cost. You must find the right balance between the controller’s price, the maximum product capacity, and user requirements for capacity. What’s more, the controller’s technical abilities are ultimately limited by a very physical problem: Dies that are part of taller stacks crack more easily, slowing down the manufacturing process.

A number of factors should be considered in order to provide customers with the best product: NAND flash evolution, signal integrity, latency, ECC capability, power, die size, and more. The knowledge of how to balance all those elements is key to achieving the highest level of performance—speed, capacity, agility, and quality.

Rex Kuo is a senior product and project engineer at Phison Electronics Corp. Kuo can be reached at rex_kuo@phison.com.

LEGO is a trademark of the LEGO Group. ©2010, 2017 The LEGO Group

© SD Association. All rights reserved. SD, SDHC, miniSDHC, microSDHC, SDXC and microSDXC Logos are trademarks of SD-3C LLC